Học viên chương trình V-STT học tập, nghiên cứu với giảng viên quốc tế về công nghệ lắng đọng đơn lớp nguyên tử

Các học viên khóa I của chương trình học bổng VNU-Samsung Technology Track (V-STT) được lắng nghe bài giảng về công nghệ Lắng đọng Đơn lớp Nguyên tử (ALD) do ông Tom Aarnink, Kỹ sư trưởng tại Phòng thí nghiệm Nano thuộc Đại học Kỹ thuật Twente, Hà Lan trình bày vào ngày 5/2/2025 và ngày 13/2/2025. V-STT là chương trình học bổng được ký kết giữa Trường Đại học Công nghệ, Đại học Quốc gia Hà Nội (VNU-UET) và Samsung Electronics Hàn Quốc.

GS.TS Chử Đức Trình – Hiệu trưởng Trường ĐH Công nghệ (bên trái ảnh) đón tiếp ông Tom Aarnink, Kỹ sư trưởng tại Phòng thí nghiệm Nano thuộc Đại học Kỹ thuật Twente, Hà Lan

Chương trình với mục tiêu phát triển nguồn nhân lực chất lượng cao trình độ Thạc sỹ trong lĩnh vực bán dẫn và vi mạch. Bên cạnh chương trình đào tạo theo chuẩn quốc tế lĩnh vực bán dẫn và vi mạch với sự tham gia giảng dạy của giảng viên Trường ĐH Công nghệ, các học viên còn được tham gia môi trường quốc tế thông qua các môn học, bài giảng bởi giáo sư quốc tế đến từ Mỹ, Hà Lan…

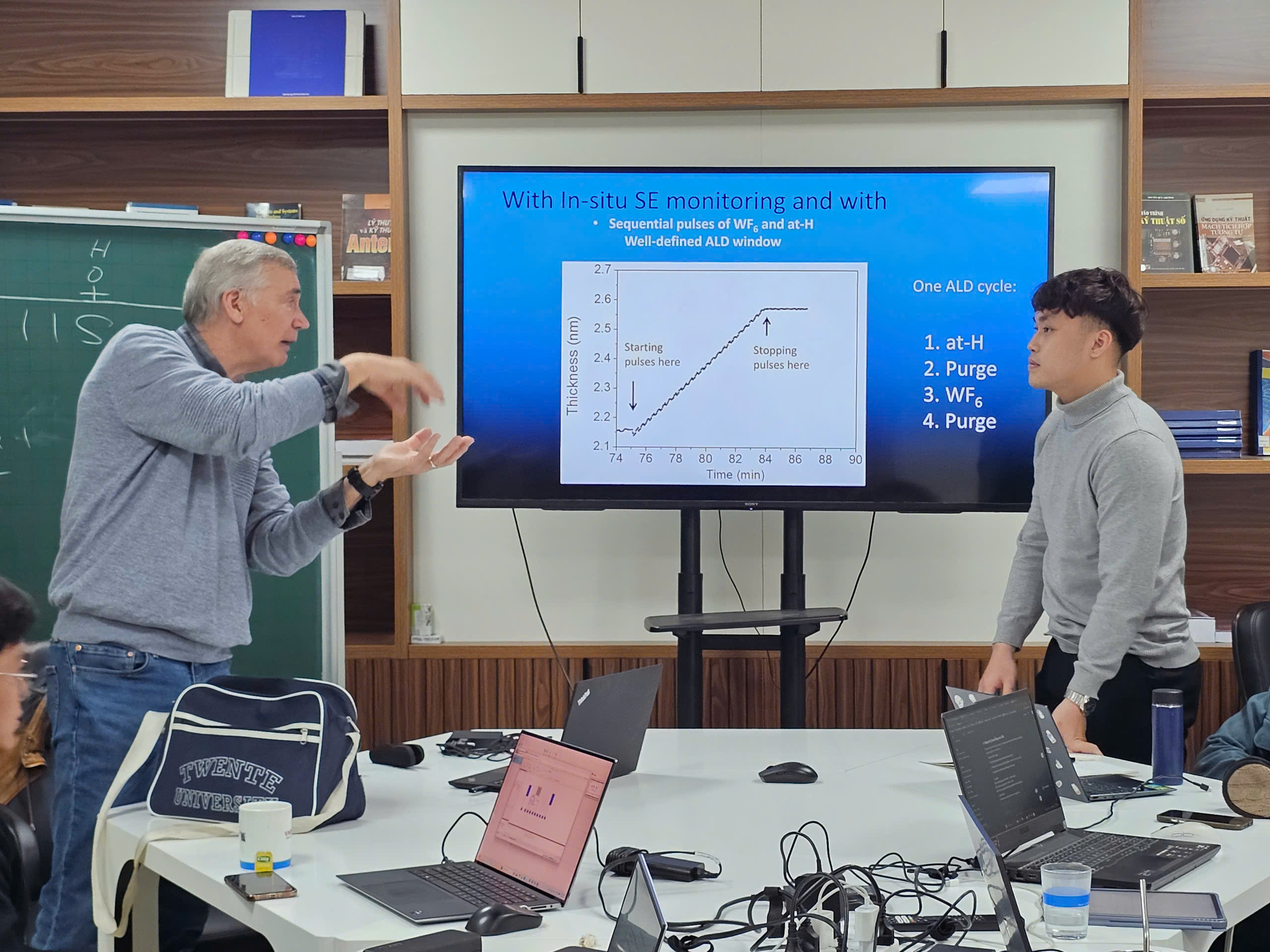

Bài giảng của ông Tom Aarnink đem lại những kiến thức thực tiễn đối với học viên khóa I chương trình V-STT

Bằng kinh nghiệm giảng dạy và làm việc tại nhiều quốc gia, ông Tom Aarnink đã truyền cảm hứng học tập cho học viên chương trình V-STT thông qua những kiến thức và kỹ năng từ thực tiễn. Bài giảng của ông Tom Aarnink về công nghệ Lắng đọng Đơn lớp Nguyên tử (ALD) mang thông điệp mạnh mẽ về sự phát triển nhanh chóng của công nghệ hỗ trợ trong lĩnh vực sản xuất bán dẫn, cũng như chỉ ra tầm quan trọng của các ngành học có liên quan tới sản xuất bán dẫn như vật lý, cơ điện tử, kỹ thuật điện tử, công nghệ tin học và kỹ thuật hoá học. Khi kích thước một con chip bán dẫn giảm xuống rất nhỏ, ở kích thước 1 nano mét trong một vài năm tới đây (để dễ tưởng tượng 1 nano met có kích thước bằng 1/100,000 sợi tóc của con người), đòi hỏi các bộ phận cấu thành con chíp cũng phải giảm xuống rất nhiều, nhỏ hơn 1 nano mét, và ở kích thước nguyên tử. Công nghệ ALD cho phép chế tạo các lớp vật liệu với độ dài chỉ vài lớp nguyên tử. Ngoài những giờ học về công nghệ ALD, học viên còn được cung cấp thêm một số kiến thức bổ trợ về công nghệ chế tạo vi mạch trong phòng sạch bán dẫn.

Kỹ sư Tom Aarnink có hơn 40 năm kinh nghiệm trong lĩnh vực chế tạo vi mạch và là một trong những chuyên gia hàng đầu trong phát triển các thiết bị công đoạn, thiết bị màng mỏng phụ vụ sản xuất bán dẫn tại châu Âu. Ông đã gắn bó và hỗ trợ các trường đại học Việt Nam từ 1995 trở lại đây trong lĩnh vực đào tạo nhân lực cho ngành bán dẫn. Năm 2017, Ông được Bộ Giáo dục và Đào tạo tặng kỷ niệm chương vì sự nghiệp giáo dục Việt Nam. Hiện nay, Ông đang là thành viên của Ban Tư vấn Quốc tế về định hướng Bán dẫn của Trường ĐH Công nghệ, ĐH Quốc gia Hà Nội.

Chương trình V-STT tuyển sinh khóa II đã khởi động với kế hoạch tuyển sinh khóa 2025 bao gồm:

– Đối tượng: Sinh viên đã tốt nghiệp (trong vòng 3 năm), sinh viên năm cuối các chương trình liên quan đến lĩnh vực bán dẫn và vi mạch

– Thành tích học tập: GPA ≥3.3/4.0

– Nộp hồ sơ: Mở đơn đăng ký từ nay đến 31/3/2025

– Phỏng vấn (bằng tiếng Anh) bởi đại diện Samsung Electronics: Giữa tháng 5/2025

– Thông báo kết quả: tháng 6/2025

– Nhập học: theo lịch ĐHQGHN.

Link nộp hồ sơ ứng tuyển:

Thông tin liên hệ:

Khoa Điện tử – Viễn thông, Trường Đại học Công nghệ, ĐHQG Hà Nội

Địa chỉ: nhà G2, 144 Xuân Thủy, Cầu Giấy, Hà Nội

Email: vstt@vnu.edu.vn

Hotline: 0984789794

https://www.facebook.com/hocbongvstt

(UET-News)